MOS の雑音(ノイズ)

雑音(ノイズ)。これは、回路設計者にとって非常に厄介な代物です。設計時に何とか小さく抑えたつもりでも、実際に LSI を作ってみると予想外に大きな雑音が見える。自分の頭の中では低雑音のアナログ回路を設計したつもりでも、シミュレーションをしてみると何処(いずこ)からか雑音が入り込んでいる。そんなことばかりが続くと、理論的に雑音を抑えることは不可能で、色々なパラメータや回路構成の LSI を実際に作って測ってみないと分からないんじゃないかと、だんだん気持ちが萎えてきます。

確かに、雑音の種類によっては理論的に計算することが難しいものもあります。しかしその一方で、ほとんど手計算だけで見積もることができるような雑音もあるのです。雑音が小さくなるように一生懸命設計しても、製造してみると結局他の雑音が支配的になってしまうかもしれません。しかし、100 % 自分の思い通りにならないからといって何も対策を打たないようでは、プロのアナログ回路設計者とは言えないのではないでしょうか。まずは手が届くところをきっちり設計することが大切です。

このページでは、最低限覚えておくべき MOS の雑音をご紹介します。ただその前に、「雑音」という言葉には2つの全く違う現象が含まれているということを、お伝えしておきたいと思います。雑音は、設計する回路自身の各素子が発生する「電子雑音」と、回路の周囲から漏れ込んでくる「外来雑音」の2つに分類することができます。電子雑音は、(ファウンダリが提供する SPICE パラメータが正しければ)シミュレーションによって比較的正確に見積もることが可能です。一方で、外来雑音は、シミュレーションで見積もることは簡単ではありません。外来雑音は、LSI 内部の配線の電位が揺れることによるものや、素子間や配線間の容量を介して伝搬するもの、そして LSI 内部の他の回路ブロックや LSI 外部の回路や環境から空中の電磁場を介して侵入するものなど、実に多彩です。最近はこれらの外来雑音を見積もるシミュレータも開発されていますが、非常に高価です。たとえそのシミュレータを使うことができたとしても、1回のシミュレーションには極めて長い時間がかかります。よって、外来雑音を定量的に小さく抑えた設計をするのは、簡単ではありません。ですからせめて、比較的簡単に見積もることのできる「電子雑音」だけでも、きっちり把握しておきましょう。

MOS 自身が発する電子雑音は、熱雑音、1/f 雑音(フリッカ雑音)、ショット雑音の3つです。このうちショット雑音は、当面覚える必要はありません。ショット雑音は、バイポーラトランジスタでは無視し得ない大きさになりますが、MOSFET では熱雑音と 1/f 雑音の中に埋もれてしまうため、通常のアナログ CMOS 回路の設計では考慮する必要がほとんどないからです。ショット雑音は、キャリアが PN 接合のポテンシャル障壁を越えようとする時に発生します。半導体の奥深くでキャリアが流れるバイポーラトランジスタでは、キャリアの流れる密度に対して PN 接合面の面積が比較的大きくなるために、ショット雑音が相対的に大きくなります。一方で、MOSFET では 1/f 雑音が支配的になります。1/f 雑音は、ゲート酸化膜とシリコン基板の境目に出来たエネルギー準位に、キャリアが不規則にトラップされることで発生します。MOSFET では、キャリアのほとんどがシリコン基板の表面を流れ、半導体の奥深くを流れることはありません。そのために、表面近くで発生する 1/f 雑音の影響を受けやすくなっています。

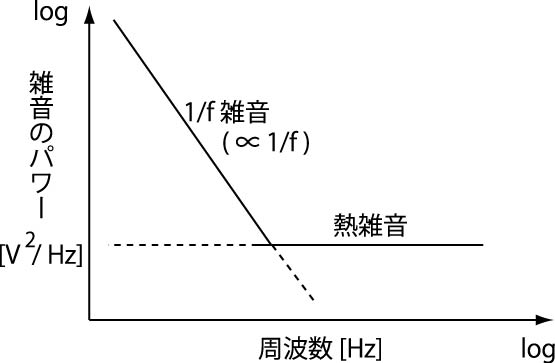

1/f 雑音は、その名の通り、周波数に反比例した大きさを持ちます。実は、何故 1/f の形になるかは、はっきりと解明されていません。科学的根拠が全て解き明かされてはいないのですが、測定してみると 1/f の形になるので、1/f 雑音と名付けられた訳です。1/f 雑音は、横軸に周波数 [Hz]、縦軸に雑音のパワー [V^2/Hz] をとって両軸を log で表示すると、上図のように奇麗な直線になります。雑音は、周波数に対する確率分布として与えられますので、雑音の単位は、横軸の単位である Hz で割って [V^2/Hz] となります。確率分布の考え方は、機会があれば当サイトでも取り上げてみたいと思いますが、優れた参考書が数多く出版されていますので、そちらをご参照下さい。(「計測における誤差解析入門」がおすすめです。)電圧の2乗として表すのは、回路の雑音は元々パワー(電力)として定義されているからです。パワーを直接測定することはほとんどありませんので、電圧を使って表現するのが慣例となっています。なお、場合によっては電流の2乗 [A^2 /Hz] で表現する場合もありますので、頭の片隅に入れて置くとよいでしょう。

MOS の 1/f 雑音は、最も簡単なモデルでは、V^2 = Kf / (Cox W L f ) [V^2/Hz] と表されます。Kf は比例定数、Cox は面積当たりのゲート容量、W はゲート幅、L はゲート長、f は周波数です。式から明らかなように、1/f 雑音を小さくするためには、MOS のサイズ(W と L)を大きくすれば良いのです。設計したアナログ回路に対して雑音の SPICE シミュレーションを実行してみて、要求仕様よりも上回るようであれば MOS のサイズを大きくしましょう。その結果、どうも現実的なサイズよりも大きくなってしまうようであれば、回路構成あるいは仕様自体を見直さなければいけません。ただし、ここで1つ注意が必要です。それは、MOS の 1/f 雑音が、全てのプロセスの SPICE パラメータに含まれているとは限らない、ということです。SPICE パラメータの中で、kf というパラメータを探してみて下さい。これが 10^-36 のようにとんでもなく小さな値が入っている場合、残念ながらその SPICE パラメータでは 1/f 雑音をシミュレーションで評価することはできません。プロセスによっては 1/f 雑音をサポートしていない場合もあるので、ご注意ください。

MOSFET の雑音の中で、もう1つ覚えておかなくてはいけないのは、熱雑音です。MOSFET の前に、普通の抵抗器の熱雑音を覚えておきましょう。熱雑音は、導体中の電子に熱エネルギーが与えられ、電子がランダムに運動することで発生します。よって、温度が高ければ高いほど熱雑音は大きくなります。雑音の式は比較的シンプルで、V^2 = 4kTR [V^2/Hz] です。k はボルツマン定数、T は温度、R は抵抗値です。これは、とにかく暗記しておいてください。余談ではありますが、ボルツマン定数は温度とセットで登場することが多く、kT と書いて温度に由来するエネルギーを示すことがよくあります。k の値は暗記する必要はありません。具体的な数値が必要になったら、google の検索画面で k と打ち込んでみてください。親切に単位まで含めて表示してくれます。

熱雑音は、周波数には依存しません。上の図に示したように、どこまでもフラットです。その特性から、熱雑音は「白色雑音(ホワイトノイズ)」と言われます。これは、太陽の光がそうであるように、光の色(周波数)を均等に混ぜ合わせると白い光に見えることに由来しています。白色雑音は、無限に大きい周波数でも一定値を保つため、そのまま周波数で積分すると発散してしまいます。しかし、実際の回路では至る所に寄生容量 C があるため、雑音の発生源である抵抗値 R とともに形成されるローパスフィルターによって帯域が制限され、積分結果が発散することはありません。現実の世界で見える雑音の大きさは積分結果で決まるため、熱雑音がどれだけ回路に影響するかは寄生容量 C に委ねられます。白色雑音を小さく抑えるように回路を設計する場合には、4kTR の中の温度と抵抗値を下げることよりも、周辺の容量値 C を大きくして帯域を下げることの方が効果的な場合があるということを覚えておきましょう。

それでは、本題の MOSFET の熱雑音に入りましょう。普通の抵抗器との違いは、導体であるか半導体であるかです。半導体は導体ほど単純な構造ではないため、多少の補正が必要になります。補正の量は、トランスコンダクタンス gm と ON 抵抗 Ro で表現でき、2/3 gm Ro であることが、昔の研究の成果によって分かっています。これを使って、 MOSFET の熱雑音は、V^2 = 4kTRo (2/3 gm Ro) = 8/3 kT gm Ro^2 となるのです。

雑音について色々書きましたが、全てを覚える必要はありません。最低限次のことだけを覚えてください。

(1)抵抗器の熱雑音は V^2 = 4kTR [V^2/Hz] である。

(2)MOSFET の雑音は、1/f 雑音と熱雑音で、上図のような周波数特性を示す。

(3)1/f 雑音を小さくするためには、MOS の面積を大きくする。

(4)熱雑音を小さくするためには、周囲の回路の帯域を下げる。

「インピーダンス」へ